Scaling aligned carbon nanotube transistors to a sub-10 nm node

Published in Electrical & Electronic Engineering

Carbon nanotubes have attracted significant interest due to their unique geometric configuration and electronic properties. They have demonstrated excellent performance and scaling behavior, surpassing traditional silicon CMOS transistors. Previous challenges in scalable fabrication have been overcome through advancements in semiconducting purity and alignment of CNT materials. Aligned carbon nanotubes (A-CNT) FETs with scaled gate lengths have been achieved, exhibiting practical performance comparable to silicon transistors. However, the large contacted gate pitch (CGP) of typical A-CNT FETs has limited their integration density and prevented the realization of predicted advantages.

In our recent study published in Nature Electronics, we fabricated A-CNT FETs with a contacted gate pitch of 175 nm, achieved by scaling the gate length and contact length to 85 nm and 80 nm, respectively. Remarkably, the A-CNT FET exhibited an impressive on-current of 2.24 mA μm-1 and a peak transconductance of 1.64 mS μm-1, surpassing the size and electronic performance of silicon 45 nm node transistors (Fig.1).

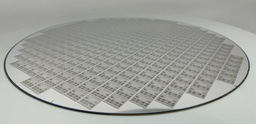

Furthermore, we showed a six-transistor static random-access memory (SRAM) cell by these ultra-scaled A-CNT FETs, demonstrating a total area (0.976 μm2) comparable to the 90 nm node (1 μm2) of silicon CMOS technology. Additionally, the A-CNT SRAM cells consumed significantly less power compared to their silicon counterparts. Overall, the 90 nm node A-CNT technology exhibited higher integration density and performance than the 90 nm node of silicon technology and holds promise for further advancements (Fig.2).

To further enhance the performance and reduce dependence on the contact length, we introduced a full-contact structure between the metal and nanotubes. The full-contact structure combined the carrier injection mechanism of side contact and end contact, i.e., the carriers can be injected from the metal to CNTs at the side (length-dependent) and at the edge (length-independent). Therefore, the full-contact A-CNT/metal junction exhibited lower contact resistance than the side-contact or end-contact junctions while maintaining a weaker contact length dependence. This enables aligned CNT FETs to be further downscaled to CGP below 55 nm (corresponding to the 10 nm technology node), while outperforming 10 nm node silicon transistors due to their high carrier mobility and Fermi velocity. These results illustrated the potential of A-CNT FETs for high-performance digital ICs at sub-10 nm nodes and provides flexibility for the trade-off between the gate length and contact length for further whole downsizing (Fig.3).

More details on this study can be found in our recent article " Scaling aligned carbon nanotube transistors to a sub-10 nm node " published in Nature Electronics. (https://www.nature.com/articles/s41928-023-00983-3)

Follow the Topic

-

Nature Electronics

This journal publishes both fundamental and applied research across all areas of electronics, from the study of novel phenomena and devices, to the design, construction and wider application of electronic circuits.

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in