Nanowire with integrated resistive memory (RRAM) to enable the supercomputers of the future

Published in Electrical & Electronic Engineering

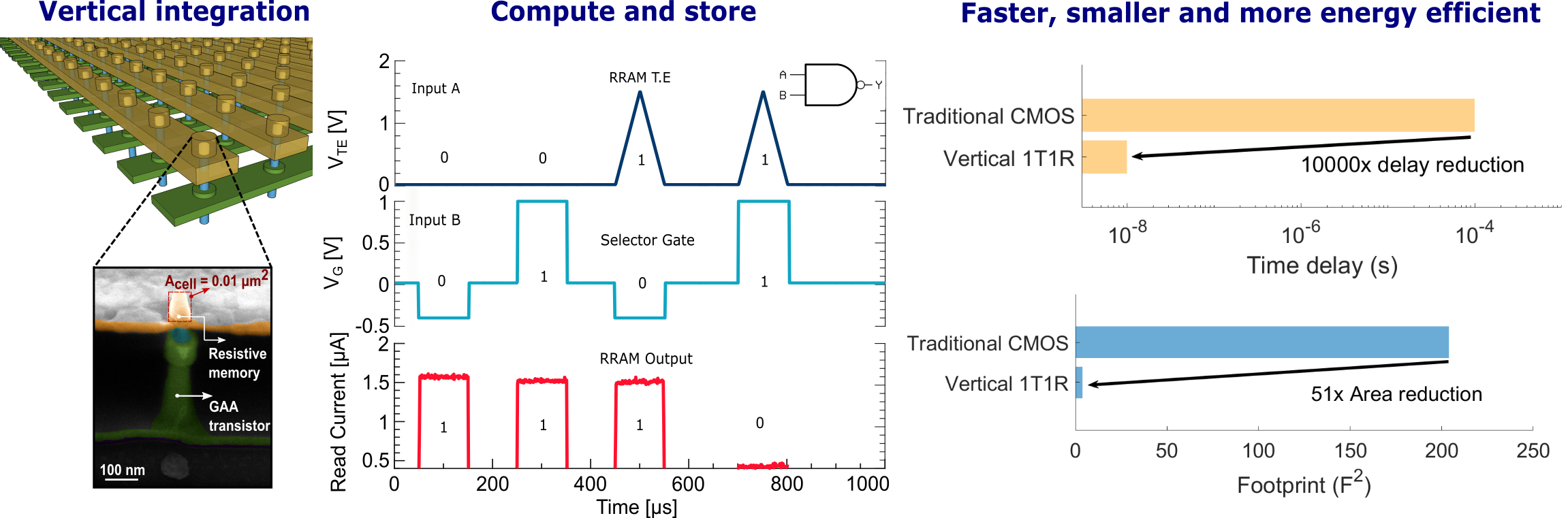

A long-standing bottleneck in technology development has been how to get processors and memories to work together faster. Now, researchers at Lund University have presented a new solution where a III-V resistive memory cell is integrated on a III-V transistor vertically, so that computation can be performed and stored much faster.

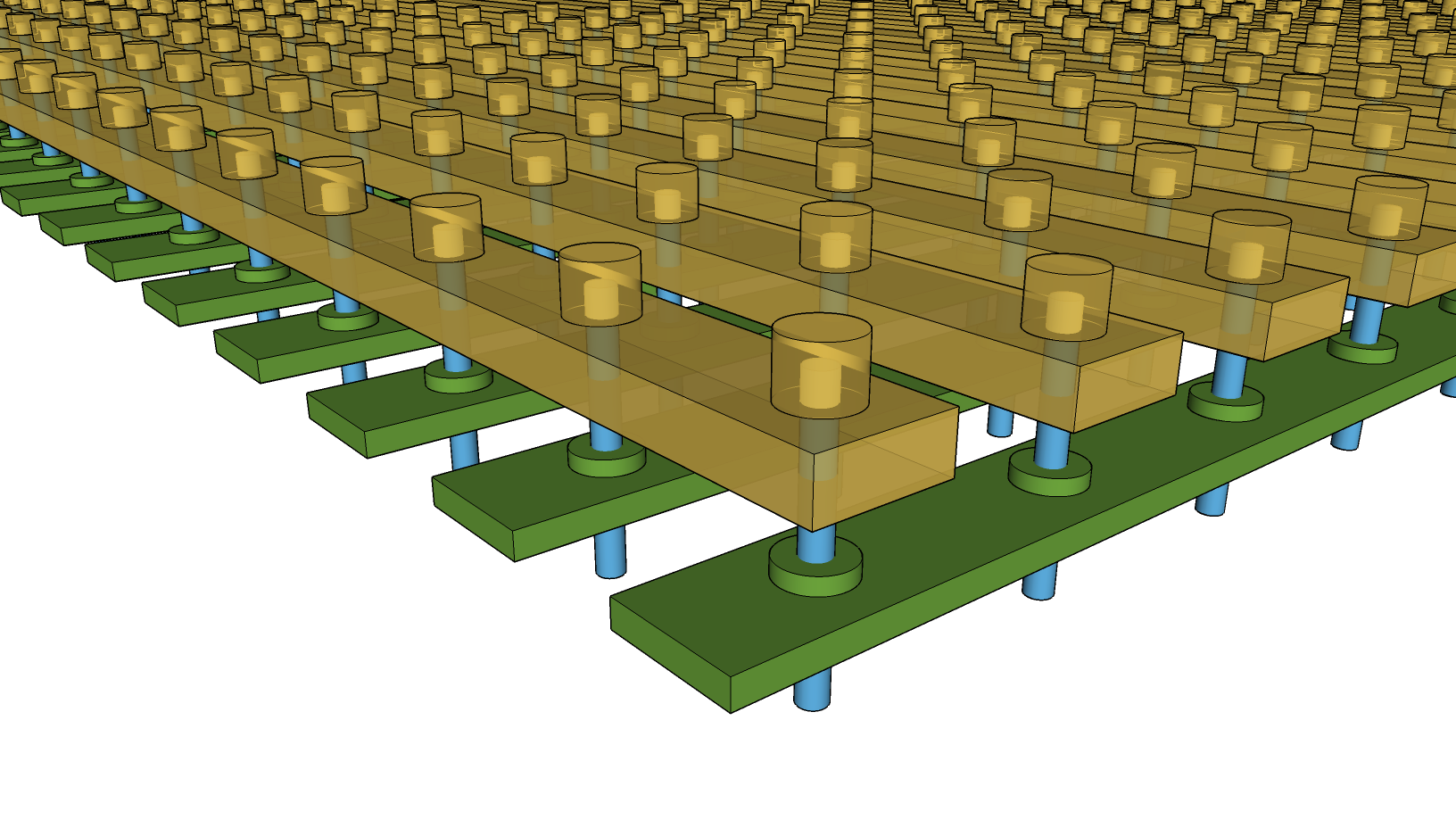

In an article in Nature Electronics, the researchers describe the so-called 1T1R configuration, where a memory cell is integrated with a vertical transistor selector by utilizing the III-V/high-k interface for both devices . This leads to improvements in scalability, speed and energy efficiency compared to today's mass storage solutions.

The basic question is that applications that require handling large amounts of data, such as AI and machine learning, need ever larger and faster capacity. For this to succeed, the memory and processor that store and perform computations need to be as close to each other as possible. In addition, the computations need to be able to be performed energy-efficiently as today's technology generates high temperatures at high loads.

''Processors have been developing rapidly for many years. On the memory side, the development has not kept up with processors.'', says Saketh Ram Mamidala, doctoral student in nanoelectronics at Lund University and the first author of the published article in Nature Electronics.

The problem that processors' computations occur much faster than memory speed has been well known for many years. In technical terms, it is called the "von Neumann bottleneck", and is caused by the memory and calculation units being separate and takes time to send information back and forth via a so-called bus, which limits the speed.

''Our version is a nanowire with a transistor at the bottom and a very small memory element that sits on top of the same wire. The idea has existed before, but it has been difficult to get performance. But we are now showing that you can get it and that it works surprisingly well'', says Lars-Erik Wernersson, professor of Nanoelectronics.

The memory cell that the researchers are working with is RRAM (Resistive Random Access Memory) and is not in itself new, but the new thing is how to succeed in functionally integrating both devices on the same nanowire that creates great opportunities.

''The resistive memory retains information even without a power supply as it is non-volatile, Saketh Ram Mamidala emphasizes.

''It is certainly possible to find solutions in silicon as well, which is the most common material, but in our case this is what creates the performance. We want to pave the way for industry with our research'', says Lars-Erik Wernersson.

The full paper can be accessed here:

https://www.nature.com/articles/s41928-021-00688-5#Sec10

Follow the Topic

-

Nature Electronics

This journal publishes both fundamental and applied research across all areas of electronics, from the study of novel phenomena and devices, to the design, construction and wider application of electronic circuits.

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in

Very nice paper and prototype, congratulations for the excellent work ! As a constructive observation, the endurance plot could be improved by presenting one data point per cycle instead of one data point per decade (see also M. Lanza et al. ACS Nano 2021, 15, 11, 17214–17231, also available here: https://pubs.acs.org/doi/10.1021/acsnano.1c06980).

Thanks for your input!