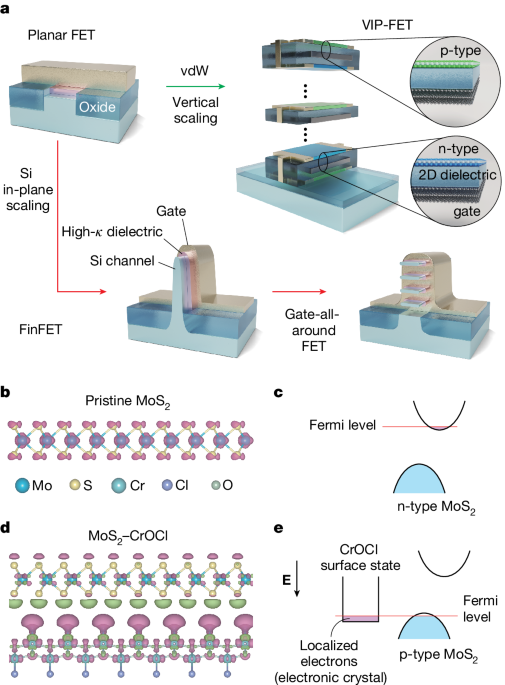

This cartoon video describes the mechanism of the van der Waals polarity-engineering of a 2D semiconductor. The n-type MoS2 transistor can be readily shifted into p-type, simply by being brought into contact with a few-layered CrOCl. Such interfacial coupling (with a quantum origin of e-e interaction) can lead to 2D p-FETs with low hysteresis, high ON current, as well as high ON-OFF ratio. The research paper "Van der Waals polarity-engineered 3D integration of 2D complementary logic" is published in Nature.

Follow the Topic

Electronic Devices

Physical Sciences > Materials Science > Materials for Devices > Electronic Devices

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in