Memristive system-on-a-chip for intelligent wireless communications

Published in Electrical & Electronic Engineering

As artificial intelligence (AI) becomes increasingly integrated into our daily lives, the hardware required to run these powerful algorithms is consuming an ever-increasing amount of energy. This growing demand makes it challenging to bring AI to energy-limited environments, such as wireless communications at the edge of networks. To address this challenge, researchers are turning to a novel computing paradigm known as analogue in-memory computing (AIMC), which is implemented with emerging electronic components like memristors. Unlike traditional computing architectures that rely on frequent data movement between separate memory and processing units, AIMC performs computations directly within memory by exploiting the fundamental laws of physics, resulting in faster and more energy-efficient processing.

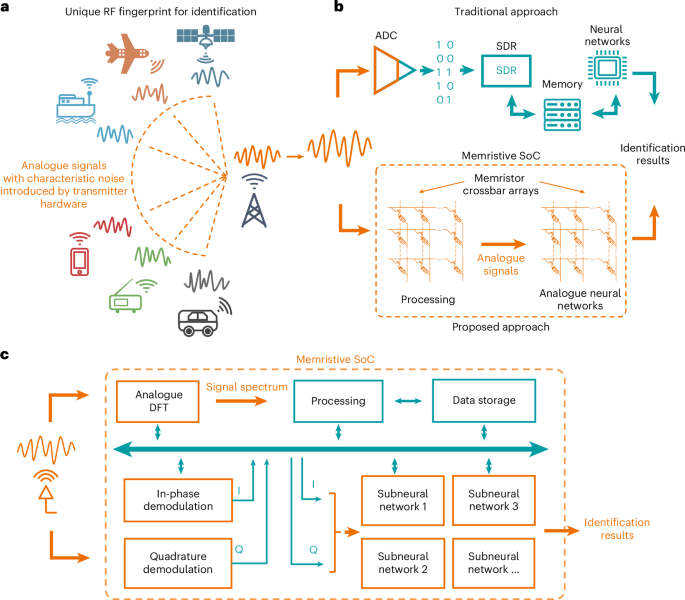

We have dedicated over a decade to advancing memristor-based AIMC hardware, from developing high-performance memristors to building system-on-a-chip (SoC) solutions. This sustained effort has culminated in our latest breakthrough: a memristive SoC that enables direct processing of analogue radiofrequency (RF) signals within memory. This system brings AI closer to the network edge, where low power consumption and high-speed processing are critical.

Hardware: from memristive devices to SoC

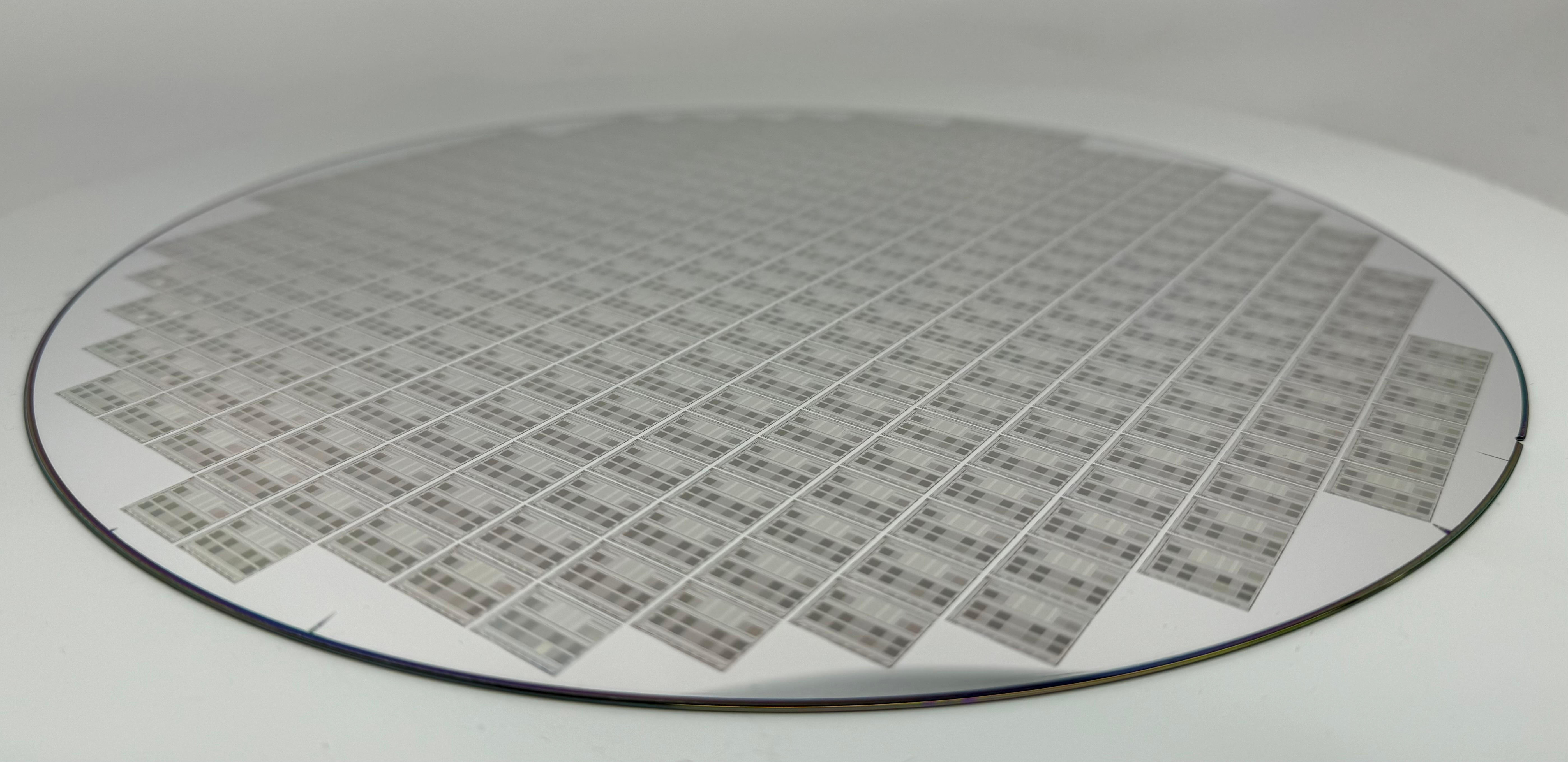

Our journey began with developing memristor devices capable of storing multiple resistance levels and retaining their states even without power1. When integrated into a crossbar array, the memristors can perform vector-matrix multiplication (VMM), a core operation in many machine learning tasks, in a single step, significantly improving computing latency and energy efficiency2. However, scaling up crossbar arrays composed solely of memristors introduces a critical challenge: sneak path currents, unintended current flows that disrupt accurate read and write operations. We adopted a one-transistor-one-memristor (1T1R) structure to suppress sneak path currents effectively. Leveraging our experience in the back-end-of-the-line (BEOL) integration of memristors with foundry-made complementary metal-oxide-semiconductor (CMOS) circuitry3, we integrated large-scale analogue 1T1R crossbar arrays4, and implemented a multilayer perceptron5, long short-term memory (LSTM) networks6, and reinforcement learning models7. These implementations powered a wide range of AI applications, including image classification5, human identification by gait6, classic control problems7, video processing8, to name a few, with peripheral circuits on external printed circuit boards. However, as we began developing memristive systems, these off-chip peripheral circuits became a bottleneck, limiting overall system latency and energy efficiency, a challenge that demands coordinated efforts from both academic research and industry.

Our early academic research and proof-of-concept demonstrations laid the foundation for the launch of TetraMem Inc., a Silicon Valley-based startup specializing in the design of next-generation AI accelerators9. TetraMem’s first-generation memristive SoC, the MX100, integrates ten memristive computing cores (crossbar arrays with on-chip peripheral circuits) with a RISC-V CPU10 and marks a significant milestone, transitioning from memristive device research to a fully integrated SoC. This product effectively bridges the gap between cutting-edge academic innovation and the practical deployment of scalable, energy-efficient AI hardware.

Applications: from AI acceleration to intelligent wireless communications

Our RF signal processing system for intelligent wireless communications is built upon algorithms and applications developed across multiple generations of our memristive hardware. Our initial application focus for memristive hardware was AI acceleration, where we proposed hardware-software co-designs to optimize the training of neural networks on memristive hardware11,12. In our early work, we also demonstrated the feasibility of using AIMC for analogue signal processing by implementing a discrete cosine transform (DCT) on the 128×64 1T1R crossbar array4. Building on the solid foundation of neural network acceleration and preliminary explorations of analogue signal processing with memristive hardware, we implemented the RF signal processing system within our memristive SoC for intelligent wireless communications. This system leverages multiple analogue memristive computing cores for both signal processing components and neural network models, enabling applications such as RF transmitter identification and anomaly detection. This demonstration benefited from our cumulative research on hardware-software co-design for memristive systems, as well as close collaboration with wireless communication experts from Texas A&M University.

Outlook

The RF signal processing system implemented in our memristive SoC marks an important first step toward using memristive hardware for intelligent wireless communications. There is plenty of room for improvement and innovation, both at the hardware and algorithm levels, to enable real-time processing of RF signals in dynamic wireless environments. At the hardware level, analogue-to-digital conversions and vice versa are still required for intermediate data transmissions between different memristive computing cores, as fully analogue on-chip communication remains a major challenge in the field. Future research enabling fully analogue inter-core communication could further enhance the latency and energy efficiency achieved in this work. At the algorithm level, our current applications are limited to static wireless environments. This limitation stems from the non-idealities of memristor devices and the limited precision of on-chip peripheral circuits, which currently hinder the implementation of algorithms and neural network models required for processing RF signals in more dynamic settings, such as those with extremely low signal-to-noise ratio (SNR) or severe channel distortions. Future research should focus on developing algorithms that not only enhance hardware precision but also compensate for inherent hardware imperfections. Such efforts will be critical for advancing signal processing capabilities in complex, real-world wireless communication environments.

References:

- Jiang, H. et al. Sub-10 nm Ta channel responsible for superior performance of a HfO2 memristor. Sci. Rep. 6, (2016).

- Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 18, 309–323 (2019).

- Xia, Q. et al. Memristor−CMOS Hybrid integrated circuits for reconfigurable logic. Nano. Lett. 9, 3640–3645 (2009).

- Li, C. et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron. 1, 52–59 (2018).

- Kiani, F., Yin, J., Wang, Z., Yang, J. J. & Xia, Q. A fully hardware-based memristive multilayer neural network. Sci. Adv. 7, 4801 (2021).

- Li, C. et al. Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 1, 49–57 (2019).

- Wang, Z. et al. Reinforcement learning with analogue memristor arrays. Nat. Electron. 2, 115–124 (2019).

- Lin, P. et al. Three-dimensional memristor circuits as complex neural networks. Nat. Electron. 3, 225–232 (2020).

- Rao, M. et al. Thousands of conductance levels in memristors integrated on CMOS. Nature 615, 823–829 (2023).

- Song, W. et al. Programming memristor arrays with arbitrarily high precision for analog computing. Science (1979) 383, 903–910 (2024).

- Li, C. et al. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. Nat. Commun. 9, 7–14 (2018).

- Wang, Z. et al. In situ training of feed-forward and recurrent convolutional memristor networks. Nat. Mach. Intell. 1, 434–442 (2019).

Follow the Topic

-

Nature Electronics

This journal publishes both fundamental and applied research across all areas of electronics, from the study of novel phenomena and devices, to the design, construction and wider application of electronic circuits.

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in