Unlocking 3D IC Performance: Cu-Cu Hybrid Bonding from Physical Mechanisms to System Integration

Published in Electrical & Electronic Engineering and Education

Key Technical Highlights

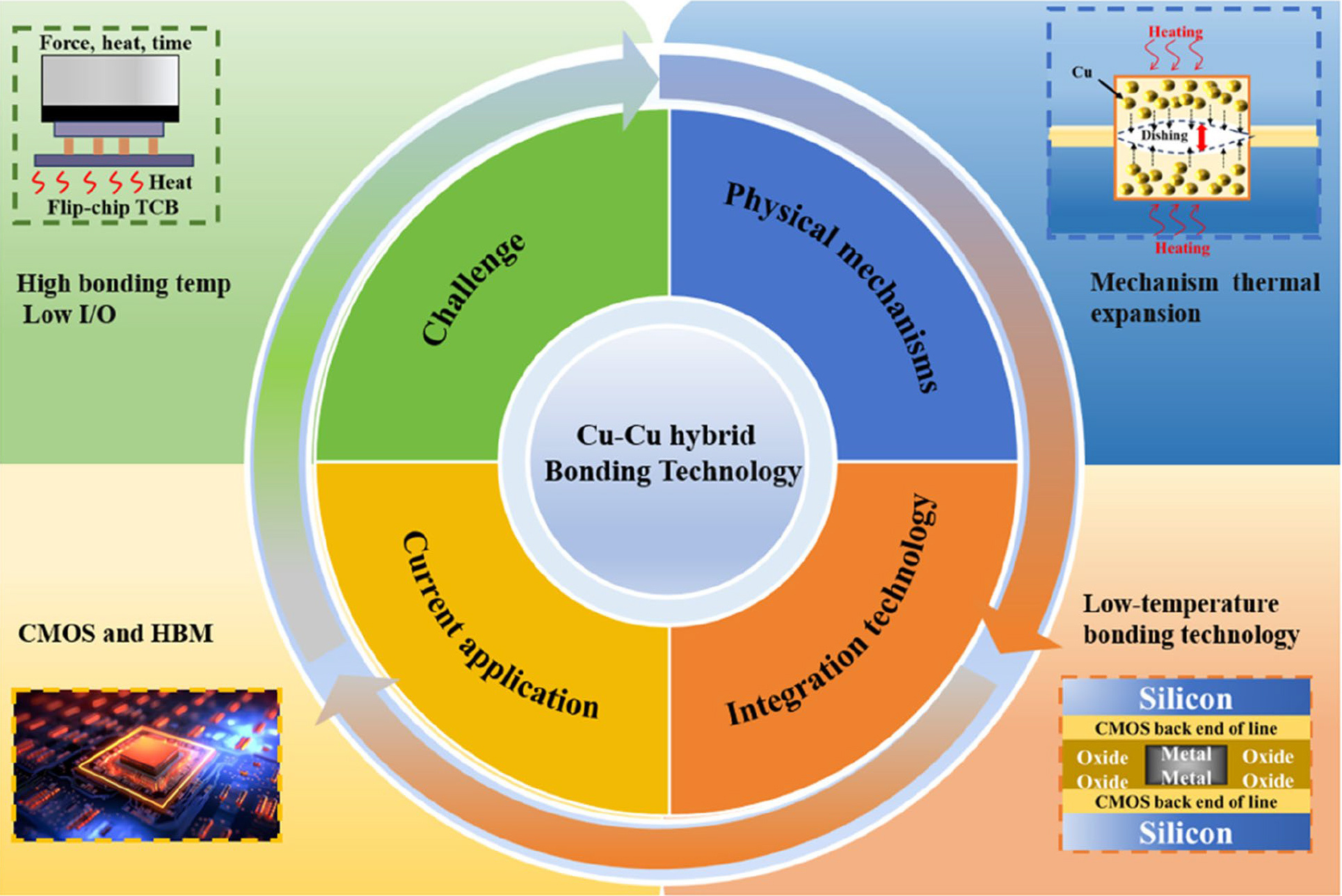

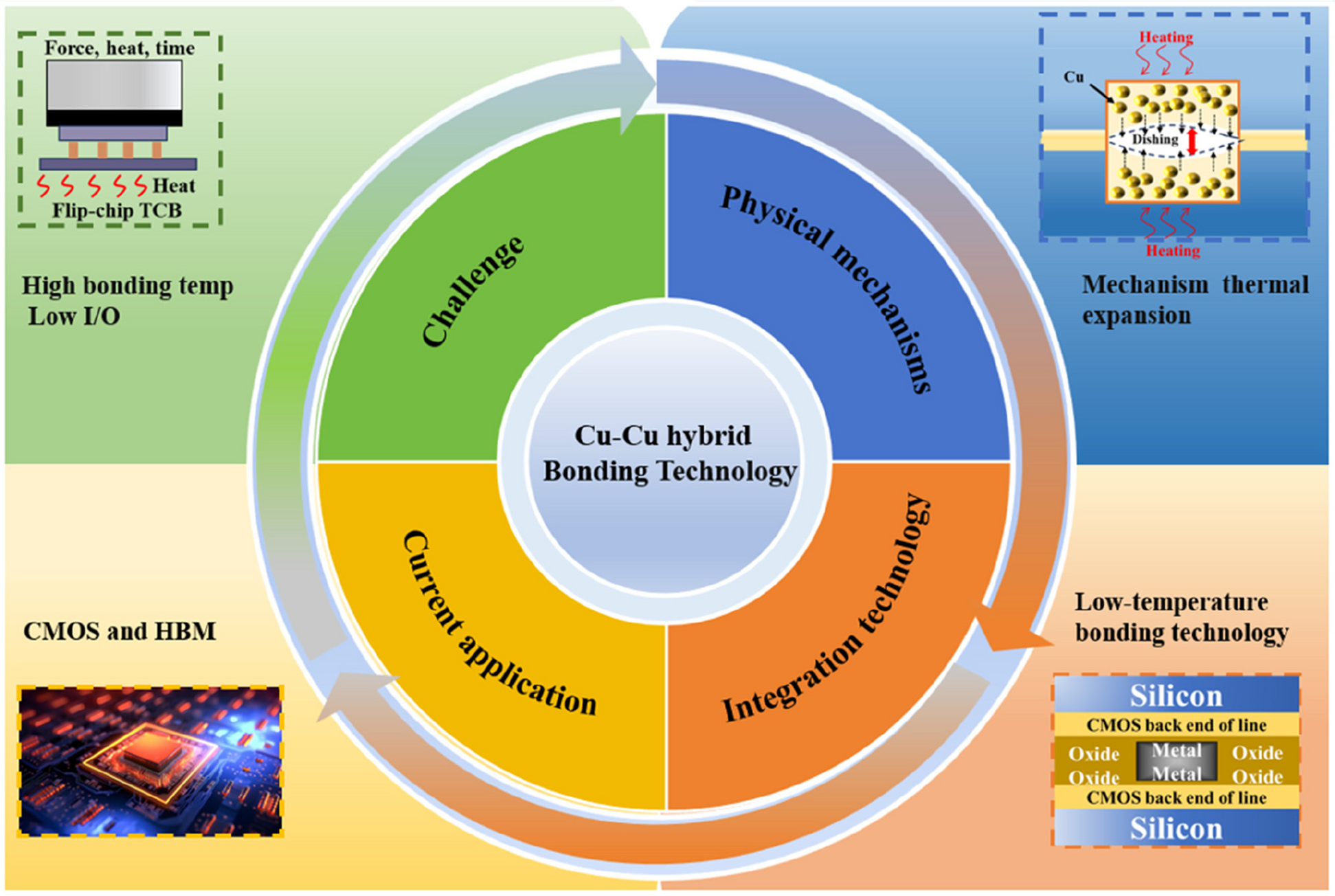

- Why it matters: Cu-Cu hybrid bonding offers ultra-fine vertical interconnect spacing, strong electrical and thermal conductivity, and a clear path beyond conventional bump-based packaging.

- Core mechanisms: The review explains both DBI-style oxide-assisted hybrid bonding and surface-activated bonding, showing how hydrophilic dielectric interfaces and copper diffusion jointly determine bond quality.

- Low-temperature progress: Passivation layers such as Ru, Pd, Ag, and Ti are helping reduce bonding temperature while suppressing oxidation and preserving interface reliability.

- Manufacturing levers: Surface planarity, CMP optimization, dielectric cleanliness, annealing control, and stress management remain decisive factors for yield and reproducibility.

- Where it is already working: The technology is advancing HBM stacking, 3D chip integration, CMOS image sensors, and GaN/Si heterogeneous integration for high-performance electronics.

Technological Implications

The review also makes the industrial picture clear: hybrid bonding is no longer just a lab concept. It is already shaping memory, imaging, advanced packaging, and next-generation power/RF systems. At the same time, challenges such as thermal boundary resistance, process complexity, alignment tolerance, and cost-efficient mass production still define the frontier.

Challenges and Future Directions

Looking ahead, the strongest opportunities lie in low-temperature bonding, higher integration density, and broader use in AI chips, HBM, and heterogeneous semiconductor platforms. For researchers and engineers working on advanced packaging, this paper provides a compact framework for connecting materials science, process engineering, and system-level design.

Toward the Future of 3D Integration

Cu-Cu hybrid bonding is rapidly evolving into a cornerstone technology for next-generation microelectronics—bridging the gap between device-level innovation and scalable 3D system integration.

Follow the Topic

-

Moore and More

This is the first top-tier journal dedicated to Beyond Moore technology in the field of integrated circuit.

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in