Efficient readout of a silicon-based quantum computer

Published in Electrical & Electronic Engineering

The problem we are facing for readout of a silicon-based quantum computer might sound simple at first, that is the readout of single electrons in a nano-scale device that form a quantum bit (qubit), but the signal originating from single electrons is very weak. Moreover, once we know how to readout a single qubit this does not mean that we can directly apply the same techniques to a quantum processor containing many qubits. The readout architecture needs to be scalable and only large scale quantum computers are capable of solving the most challenging problems that a classical computer could never solve. All quantum computing architectures face this identical problem of growing complexity and high demands of efficiency at a large scale.

Classical processors once consisted of discrete elements that were wired one by one similar to current quantum processors, but modern processors and memory devices contain billions of transistors on a small chip, yet all of these transistors are controlled only by a small number of input-output ports. While for quantum devices there are slightly different requirements, it is this reduction of complexity and high-yield nanofabrication that inspired our work. By using quantum dot (QD) devices that have been fabricated alongside classical nanowire field-effect-transistors (FET) on a silicon chip, we apply these concepts to quantum information processing at milliKelvin temperatures.

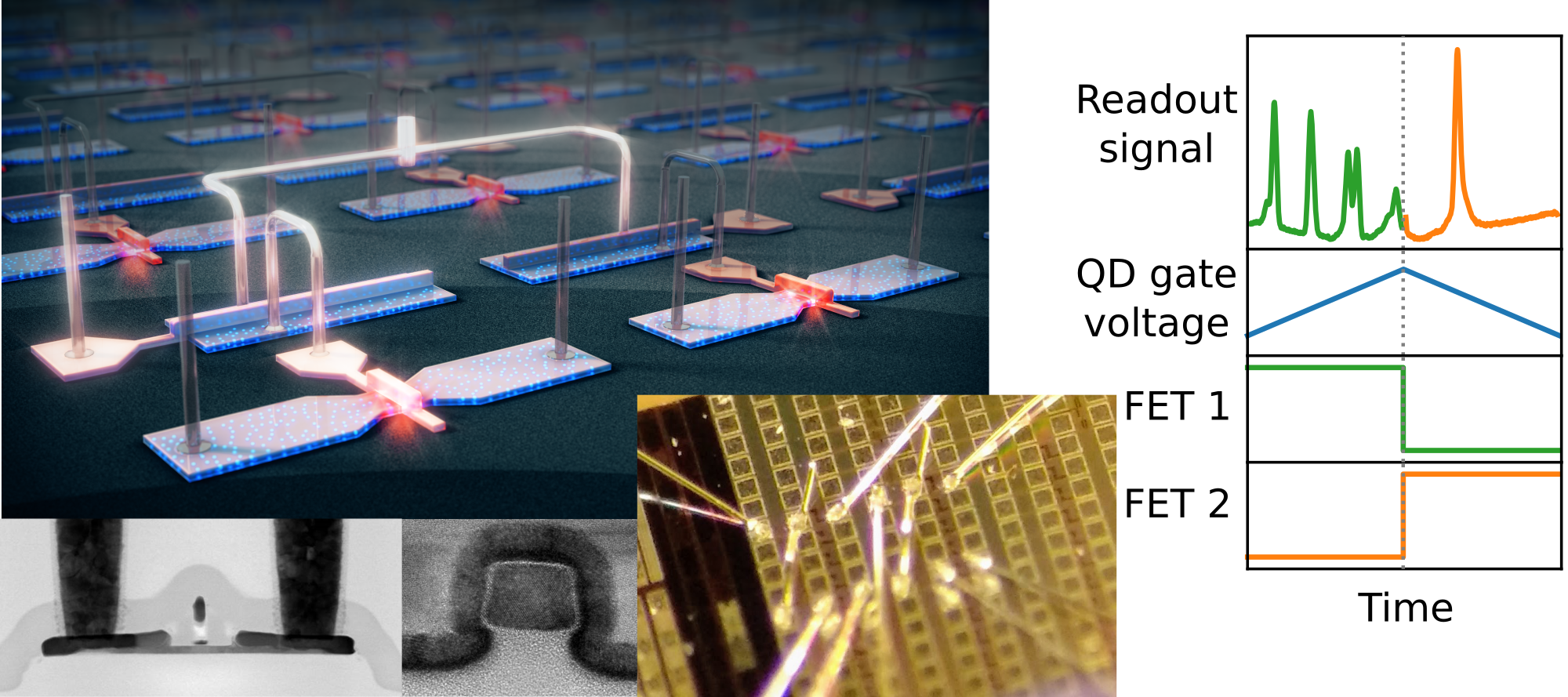

Figure: Illustration of our circuit for sequential readout of QD devices. The readout signal is passed onto the selected QD device conditional on the control FET state. The cross-sectional images of devices and the wire-bonding image show how the circuit is implemented. Using a pulse sequence, sequential readout of the circuit is shown.

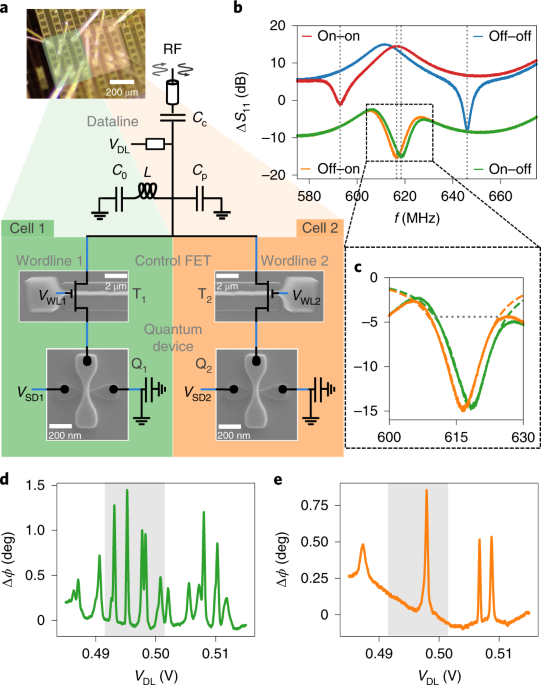

We are not the only ones to have realised that by using silicon technology as a basis for a quantum processor, many of the challenges of large scale devices could be addressed. In 2017 multiple articles working towards a blueprint of such integrated quantum-classical processors have appeared. The story behind our paper really begins at this point, as we considered how we could test some of the ideas related to readout of a large scale device on a small scale in our lab. An efficient way to readout a single QD device is by using signals that are close to the frequency at which radios operate, by coupling the quantum device to a careful engineered resonant circuit. However, one resonator per qubit is not scalable. So we started discussing ideas with our colleagues in Cambridge and decided to put concepts for addressing and charge storage found in Dynamic Random Access Memory into practice. In the first step, we connected our readout resonator to the channel of a single 10μm wide FET, via bond wires, which then conditionally passes the signal on to the gate of a short channel transistor device, via another bond wire, in which the QDs are formed. We found that the control FET still operates well at milliKelvin and we achieved conditional readout at a sensitivity comparable to direct measurements. Additionally, we observed single electron storage on the QD of the order of 1 second when the FET is operated in the off state (see Phys. Rev. App.).

In our work published in Nature Electronics, we go further than this and implement a circuit consisting of two FET and QD devices as shown in the illustration above, which allows us to actually test the key concept of dynamic readout. As you can see, bonding of this circuit turned out to be challenging, but we were able to succeed and show sequential readout of two devices, which is the basis for dynamic random access of many cells. Finally, we wanted to better understand why our circuit performed well in order to give guidelines for future designs of integrated classical-quantum circuits. We therefore look more closely into control FETs of different sizes, which were available on the same chip, and develop a model of the resistance and capacitance depending on channel width and gate length. Using a readout model, we evaluate the readout signal-to-noise ratio as a function of these scaling parameters and find that the choice we made at the beginning, of using a FET of large channel width and small gate length, was the right choice, as the low resistance of a wide channel device maximises the SNR. However, to allow readout of a large scale device efficiently the size of the FET needs to be scaled down. Our models show that the FET width can be scaled by a factor of 100 allowing dense integration while maintaining sufficient SNR by compromising on retention time and voltage noise.

If you want to learn more about this, please see our article available at Nature Electronics and our video abstract below. As a next step it would be interesting to design an integrated circuit version of our experiment following the guidelines given by our models.

Follow the Topic

-

Nature Electronics

This journal publishes both fundamental and applied research across all areas of electronics, from the study of novel phenomena and devices, to the design, construction and wider application of electronic circuits.

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in