The convergence of reconfigurable electronics and multi-valued logic systems

Published in Electrical & Electronic Engineering

The continuous pursuit of higher performance, improved efficiency, and enhanced functionality in electronic systems has driven the exploration of novel circuit designs beyond traditional fixed-function digital integrated circuits.

Reconfigurable electronics involves the design and implementation of circuits that can be modified dynamically to provide more diverse and complex calculations within a given footprint. A key strategy of this circuit operation is to integrate a memory function into the inherent switching function of transistors by employing a charge storage layer. This integration enables the diversification of the field-effect characteristics of a single transistor, thereby facilitating the implementation of multiple logic functions within a minimal circuit unit without involving complex device architecture or hardware cluster configuration.

In parallel, multi-valued logic extends the binary logic framework by introducing additional logic states. Therefore, in conjunction with reconfigurable electronics, multi-valued logic can significantly enhance data processing efficiency and integration density in traditional digital circuits. For instance, ternary logic systems offer a remarkable reduction in system complexity of approximately 63.1% (log 2/log 3) when compared to binary logic systems.

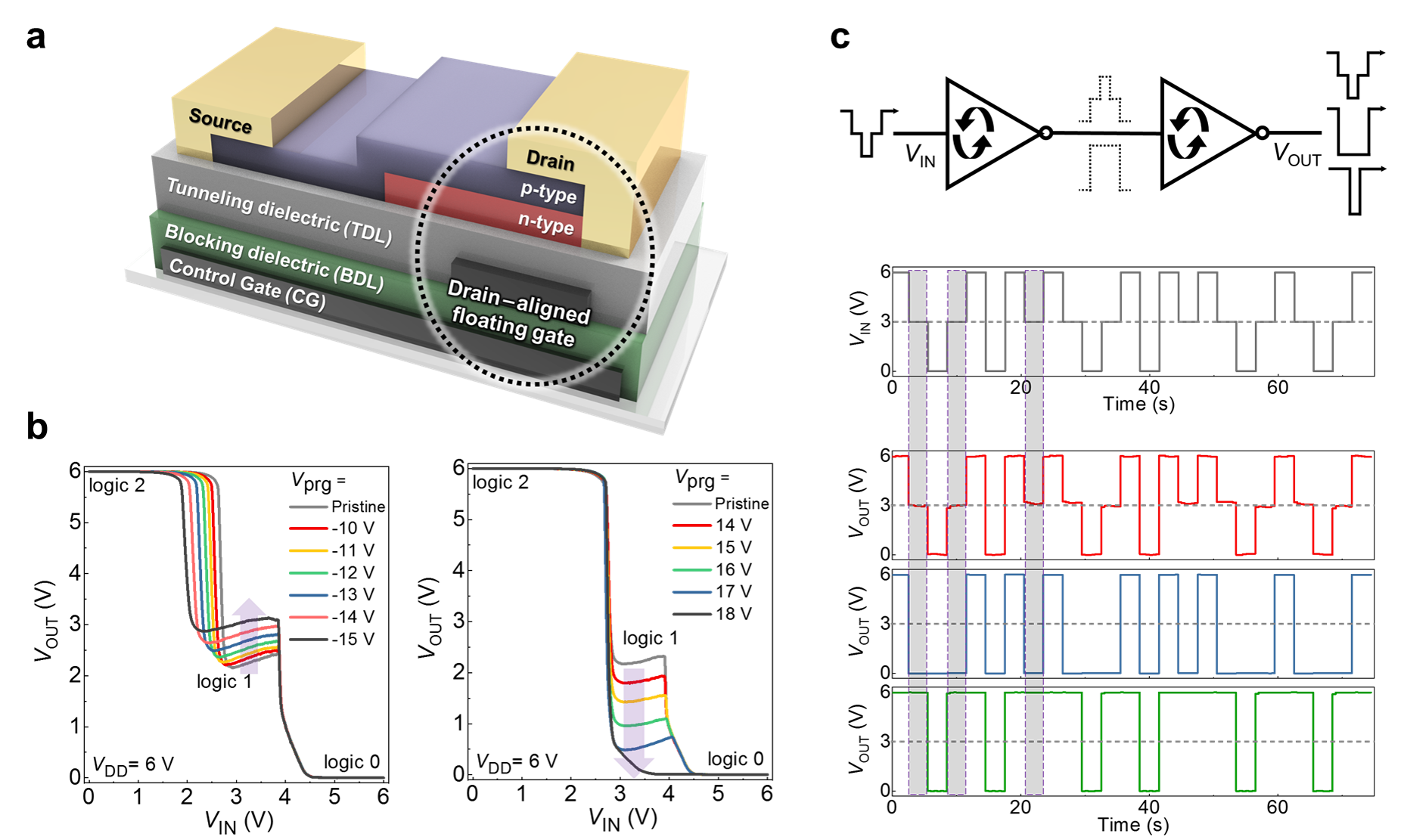

a) A schematic illustration of heterojunction non-volatile memory transistor. b) Voltage transfer characteristics of a binary/ternary reconfigurable logic inverter. c) Pulsed measurement of two-stage binary/ternary reconfigurable logic inverter with three different configurations (ternary-ternary, binary-ternary, and ternary-binary/binary-binary).

In our work published in Nature Communications, we propose the synergistic combination of reconfigurable electronics and ternary logic systems, with the aim of pioneering a new paradigm in circuit design. The dynamic nature of reconfigurable electronics offers a flexible platform for implementing high-performance ternary logic circuits and ternary-based reconfigurable logic circuits. As a building block for implementing the ternary logic circuits, we employed p/n heterojunction transistor. The p/n heterojunction transistor can show negative transconductance characteristics (NTC), allowing ternary logic systems using conventional CMOS design while maintaining the necessary number of transistors for each logic state. By incorporating `drain-aligned floating gate’ into the p/n heterojunction transistor, we developed a heterojunction non-volatile memory transistor, in which the NTC characteristics could be dynamically controlled by non-volatile memory function. With the dynamic NTC characteristics of the heterojunction non-volatile memory transistor, a binary/ternary reconfigurable logic inverter (R-inverter) was implemented successfully. The R-inverter showed an exceptionally high static noise margin of 85% for binary logic operation and 59% for ternary logic operation, as well as long-term stability and outstanding cycle endurance. A prototype of binary/ternary dynamic logic conversion-in-memory was demonstrated using a serially-connected R-inverter chain as well, which could generate three different sets of output logic signals for the same input signal in three logic levels, depending on the memory state of each constituent reconfigurable inverter.

By leveraging the dynamic characteristic of the reconfigurable electronics and the information-rich nature of multi-valued logic, we foresee that the reconfigurable multi-valued logic systems will present a compelling opportunity to revolutionize circuit design and computational efficiency of future integrated circuits. For further information, please refer to our published article "A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors" in Nature communications.

Lee, C., Lee, C., Lee, S. et al. A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors. Nat Commun 14, 3757 (2023). https://doi.org/10.1038/s41467-023-39394-5

Follow the Topic

-

Nature Communications

An open access, multidisciplinary journal dedicated to publishing high-quality research in all areas of the biological, health, physical, chemical and Earth sciences.

Related Collections

With Collections, you can get published faster and increase your visibility.

Women's Health

Publishing Model: Hybrid

Deadline: Ongoing

Biosensing

Publishing Model: Hybrid

Deadline: Jun 30, 2026

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in