Neuromorphic CMOS-MoS2 based hybrid system for low power edge-computing

Published in Electrical & Electronic Engineering

The evolution of Internet-of-Things (IoTs) and edge devices in the areas of ubiquitous learning, sensing, and human-machine interaction is increasing dramatically. These devices demand integrated intelligence in low power, small area, and computationally efficient hardware [1]. However, there are several limitations in conventional computing systems based on the von Neuman architecture. Conventional computers are often unable to manage the variability of data obtained in the real world and thus have traditionally been weak at tasks such as data prediction and classification. On the other hand, neurobiological processing systems are remarkable computational devices. Their basic computing elements, i.e., the neurons, are slow, heterogeneous and stochastic in nature, and yet they outperform today’s most powerful computers at real-world tasks such as vision, audition, and motor control. When compared with digital computers, the brain consumes much less power (~20W) and is highly adaptive. The loss of merely one transistor can wreck a microprocessor, whereas the loss of neurons does not affect the functionality of the brain [2].

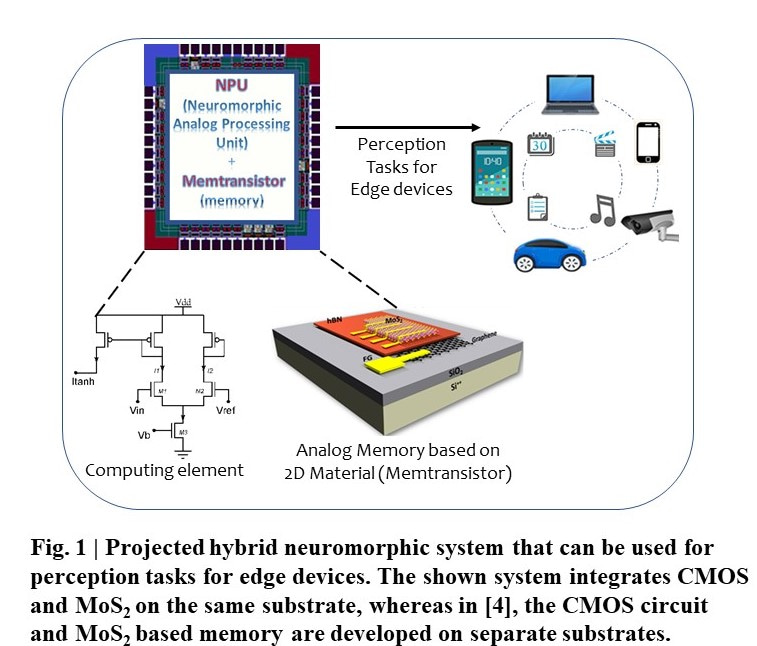

The brain can serve as a template for the next generation computational architectures. We have proposed one such hybrid architecture based on neuromorphic population coding [3], where encoding of information is carried out by the activity in an ensemble of neurons such as in the olfactory, motor, and visual cortex. Our proposed hybrid architecture [4] utilizes a CMOS-based silicon neuron as a basic computing element, and molybdenum disulphide (MoS2) based two-dimensional synaptic memtransistor as an analogue memory, instead of conventional digital memories, to avoid bottleneck in terms of power and area. Two-dimensional (2D) materials form a perfect candidate for such hybrid approach since they are immune to short channel effects while demonstrating a wide range of electronic properties. A combination of silicon technology with 2D materials can surpass the current technology limitation and can offer remarkable advancements in circuit architecture and device performance at atomic levels. In this regard, we propose a biologically inspired wake-up system [4], shown in Fig 1, with embedded intelligence and energy efficient footprint, that can be integrated with existing edge computing devices to improve their energy and performance. This system exploits the inherent mismatches present in lower silicon technology nodes to reduce computational complexity and simultaneously uses multi-state memtransistive device for low power computation and reduced computational complexity. The memtransistor used in this work is a 2D counterpart of a floating gate memory which is fabricated from a single crystalline MoS¬2 nanosheet. It utilizes temporally confined charge tunneling between the channel (MoS2) and the floating gate to attain multiple conductance states and demonstrates properties similar to those of a biological synapse [5]. In the current hybrid framework, this synaptic memtransistor memory provides two functions simultaneously, one a substitute for digital memories as an adaptable multi-state memductance and the other is the execution of an inherent multiplication operation by Kirchhoff’s current law (KCL), thus offering a low power computational paradigm.

This framework showed promising results for demonstrated regression and classification tasks [4], thus proving to be a step closer toward designing low power, smaller dimensions, fault-tolerant, and robust architecture. These characteristics enable the framework to be employed in onsite processing of data such as in IoT devices, edge devices, energy- and area-constrained devices.

Acknowledgment: A detailed explanation of the system can be found in our recently published paper at the Scientific Reports [4]. We acknowledge all the co-authors of this published paper for their contribution to the blog.

References:

1. Take it to the edge. Nat Electron 2, 1 (2019) doi:10.1038/s41928-019-0203-8

2. Thakur, C. S., et al (2018). Large-scale neuromorphic spiking array processors: A quest to mimic the brain. Frontiers in neuroscience, 12, 891.

3. Thakur, C. S., Hamilton, T. J., Wang, R., Tapson, J., & van Schaik, A. (2015, July). A neuromorphic hardware framework based on population coding. In 2015 International Joint Conference on Neural Networks (IJCNN) (pp. 1-8). IEEE.

4. Gupta, S., Kumar, P., Paul, T., van Schaik, A., Ghosh, A., & Thakur, C. S. (2019). Low Power, CMOS-MoS 2 Memtransistor based Neuromorphic Hybrid Architecture for Wake-Up Systems. Scientific Reports, 9(1), 1-9.

5. Paul, T., Ahmed, T., Tiwari, K. K., Thakur, C. S., & Ghosh, A. (2019). A high-performance MoS2 synaptic device with floating gate engineering for neuromorphic computing. 2D Materials, 6(4), 045008.

Follow the Topic

-

Scientific Reports

An open access journal publishing original research from across all areas of the natural sciences, psychology, medicine and engineering.

Related Collections

With Collections, you can get published faster and increase your visibility.

Advances in neurodegenerative diseases

Publishing Model: Hybrid

Deadline: Jun 30, 2026

AI for clinical decision-making

Publishing Model: Open Access

Deadline: Jun 23, 2026

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in

Congratulations Chetan ! Very beautiful stuff, I feel very happy for you. Well deserved !