Single-transistor-based electronic neurons and synapses

Published in Computational Sciences and Mathematics

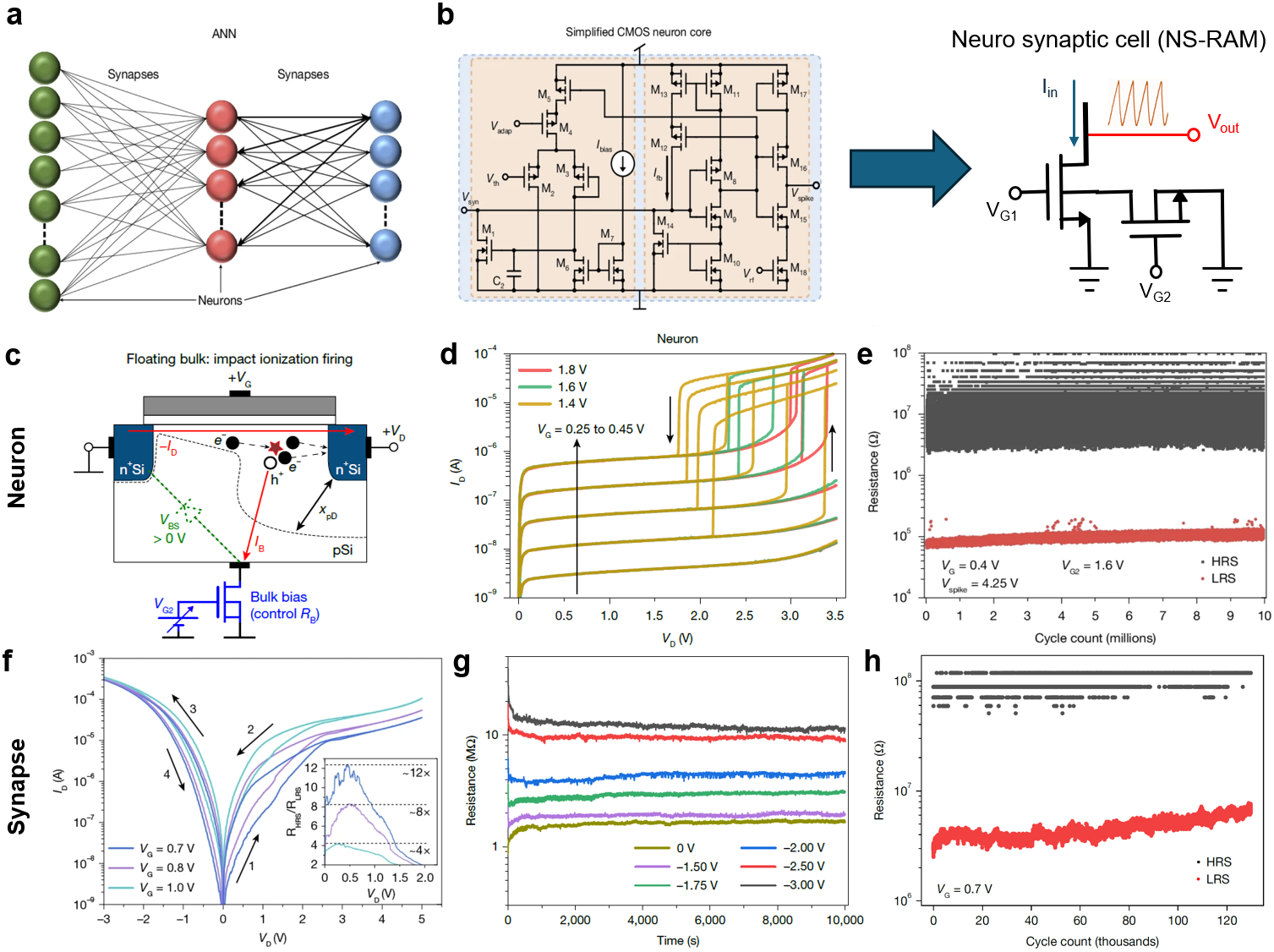

Hardware implementations of artificial neural networks (ANNs)—the most advanced of which are made of millions of electronic neurons interconnected by hundreds of millions of electronic synapses (Fig. 1a)—have achieved higher energy efficiency than classical computers in some small-scale data-intensive computing tasks1. In traditional digital CMOS VLSI neuromorphic circuits, such as Intel’s Loihi2 or IBM’s NorthPole3, neuron and synaptic circuit blocks typically involve dozens of transistors (Fig. 1a) to mimic different bio-inspired models of neural and synaptic behaviours. They rely on synchronous accumulators and comparators, dense and energy hungry memory blocks to store synaptic states, and large look-up-tables that define time-domain dynamics of each building block. Considering that an artificial neural network can comprise more than hundred-thousand neurons and tens-of-million synapses, this results in massive silicon implementations that require state-of-the-art technology nodes to be feasible (in terms of area, cost and performance).

Thus, simplifying the structure of electronic neurons and synapses can be a pathway to more efficient neuromorphic circuits. Here, we report how, leveraging on standard CMOS devices and well-known device physics (Fig. 1c), a single transistor can mimic both synaptic and neural behaviours for neuromorphic circuits. Using a simple, compact, and scalable 2-transistor cell, and electrically tailoring well-known floating body effects in standard CMOS transistors, we managed to use impact-ionization-driven avalanche and charge trapping to build an in-circuit-configurable neuro-synaptic device — the Neuro-Synaptic Random Access Memory (NS-RAM) cell (Fig. 1b).

The key lies in setting the resistance of the bulk terminal to a specific value to tailor a physical phenomenon called "punch-through impact ionisation", common to floating body MOSFET devices4 (Fig. 1c), which generates a current spike very similar to what happens when an electronic neuron is activated (Fig. 1d). This abrupt firing is controllable via a bulk-connected transistor (Fig. 1b) that allows to set the timing dynamics (i.e., integration and relaxation times, threshold potentials) to an outstanding degree for spiking neural network customization down to each neuron. This process is robust, repeatable, and based on well-known physics, providing a reliability advantage over time (Fig. 1e) compared to other emerging technologies, such as volatile memristors.

Additionally, by setting the bulk resistance to other specific values, the transistor can store charge in the gate oxide (Fig. 1f), causing the resistance of the transistor to persist over time (Fig. 1g), mimicking the behaviour of an electronic synapse. This behaviour can be sustained over >100 thousand cycles, which is better than some embedded charge-trapping memory device that rely on floating gates or trappy oxides, and on par with certain memristor technologies that are emerging in the embedded memory market. In principle, a single transistor can even replace an SRAM cell (6 transistors at least) to play the role of a binary/digital synapse, incurring into huge area benefits.

The physical phenomenon of "impact ionisation" had traditionally been considered a failure mechanism in silicon transistors, but our team has managed to control it and turn it into a highly valuable application for the industry. This approach opens a huge window of opportunity for neuromorphic device and circuit design by exploiting almost any CMOS technology out there, making it an attractive application for the industry. The possibilities are endless, and I find that very exciting! I hope you enjoy the paper and find it exciting too😊.

References

- Mehonic, A. & Kenyon, A. J. Brain-inspired computing needs a master plan. Nature 604, 255–260 (2022).

- Orchard, G. et al. Efficient neuromorphic signal processing with Loihi 2. In Proc. 2021 IEEE Workshop on Signal Processing Systems (SiPS) (eds Sousa, L. & Sheikh, F.) 254–259 (IEEE, 2021).

- Cassidy, A. S. et al. 11.4 IBM NorthPole: an architecture for neural network inference with a 12nm chip. In Proc. 2024 IEEE International Solid-State Circuits Conference (ISSCC) Vol. 67 (ed. O’Mahony, F.) 214–215 (IEEE, 2024).

- Moselund, K. E. et al. Punch-through impact ionization MOSFET (PIMOS): from device principle to applications. Solid State Electron. 52, 1336–1344 (2008).

Follow the Topic

-

Nature

A weekly international journal publishing the finest peer-reviewed research in all fields of science and technology on the basis of its originality, importance, interdisciplinary interest, timeliness, accessibility, elegance and surprising conclusions.

Please sign in or register for FREE

If you are a registered user on Research Communities by Springer Nature, please sign in